업계는 더 이상 데스크톱 및 서버 플랫폼을 위한 차세대 DDR6 메모리 표준에서 멀지 않으며, 메모리 칩 제조업체는 JEDEC와 협력하여 관련 사양의 공식화를 추진하고 있습니다. 국내 언론 더일렉에 따르면 SK하이닉스, 삼성, 마이크론 등 주요 스토리지 제조사들은 DDR6 설계를 실험실에서 시작했으며 점차 기판 제조사들과 모듈 개발 계획을 조율하고 있다. 위에서 언급한 공동 연구 개발은 차세대 메모리가 설계 수준에서 통일된 기술 기반을 갖출 수 있도록 업계 표준 기구인 JEDEC의 주도하에 수행됩니다.

관련 제조업체는 이르면 2024년 초 JEDEC가 제공한 DDR6 표준 초안의 첫 번째 버전에 액세스할 수 있을 것으로 보고되지만 전압 범위, 신호 정의, 전력 소비 패키징 및 핀 레이아웃과 같은 주요 매개변수는 아직 확정되지 않았습니다. 최근 산업 고도화가 심화되면서 이러한 격차는 점차 메워질 것으로 예상되며, 표준 확정 과정도 가속화될 것으로 보인다. 이전에는 몇몇 주요 제조업체가 실제로 샘플 단계에서 벗어나 보다 엄격한 검증 주기에 진입하여 후속 대량 생산의 기반을 마련했습니다.

외부에서 우려하는 성능 지표를 보면, 현재 공개된 정보에 따르면 DDR6의 목표 시작 전송 속도는 8,800MT/s이며, 이를 기존 DDR5 속도 제한의 두 배에 가까운 17,600MT/s까지 확장할 계획입니다. 이러한 획기적인 속도 증가의 핵심은 DDR6이 4×24비트 하위 채널 아키텍처를 채택했다는 점이며, 이를 위해서는 신호 무결성 측면에서 새로운 설계 아이디어의 도입이 필요합니다. 대조적으로, 현재의 DDR5는 여전히 2×32비트 서브채널 구조를 사용합니다. 두 세대의 표준 간의 채널 분할 차이로 인해 컨트롤러 설계, 배선 및 PCB 레이어 수에 대한 새로운 요구 사항이 적용됩니다.

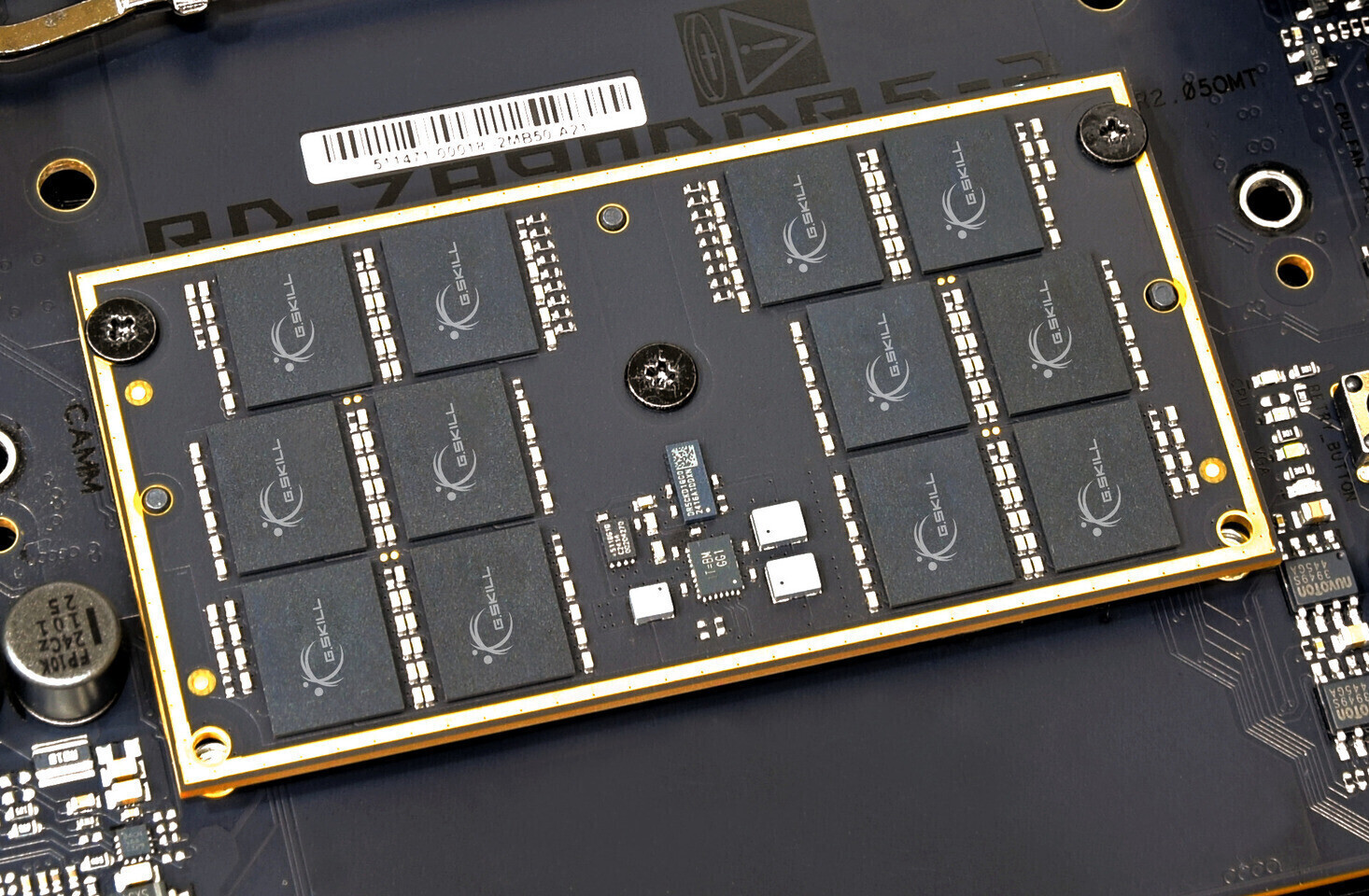

기존 DIMM 모듈이 고주파수에서 물리적 한계에 직면하는 상황에서 업계에서는 일반적으로 공간, 배선 및 인터페이스 형태에서 고속 신호의 여러 병목 현상을 완화하기 위한 CAMM2 기술에 기대를 걸고 있습니다. 현재 징후는 서버 플랫폼이 DDR6을 가장 먼저 도입한 후 생산 능력이 증가한 후 점차적으로 고급 노트북 플랫폼으로 이동할 것으로 예상된다는 것을 나타냅니다. 데스크탑 소비자 제품은 나중에 뒤따를 수 있습니다.

시간표로 볼 때 지난해 업계에서는 DDR6가 2027년에 '출시'될 것이라는 이야기가 있었습니다. 그러나 이번 판단에서는 2027년을 핵심 고객 검증 단계로 보는 경향이 더 크고, 실제 시장의 대규모 상업적 사용은 2028년에 실현될 것으로 예상됩니다. 동시에 차세대 서버의 출하 및 전체 애플리케이션 침투율로 인해 DDR5의 비중은 지난해 약 80%에 이르렀고 올해는 약 90%까지 더 오를 것으로 예상되며, 업계 체인에서 DDR4의 역할은 점차 "퇴출되는" 세대로 간주되고 있습니다. 이는 새로운 표준을 위한 더 많은 시장 공간을 확보할 뿐만 아니라 DDR6 칩 및 모듈의 후속 대량 생산을 위해 웨이퍼 공장의 생산 능력을 확보하는 데에도 도움이 됩니다.